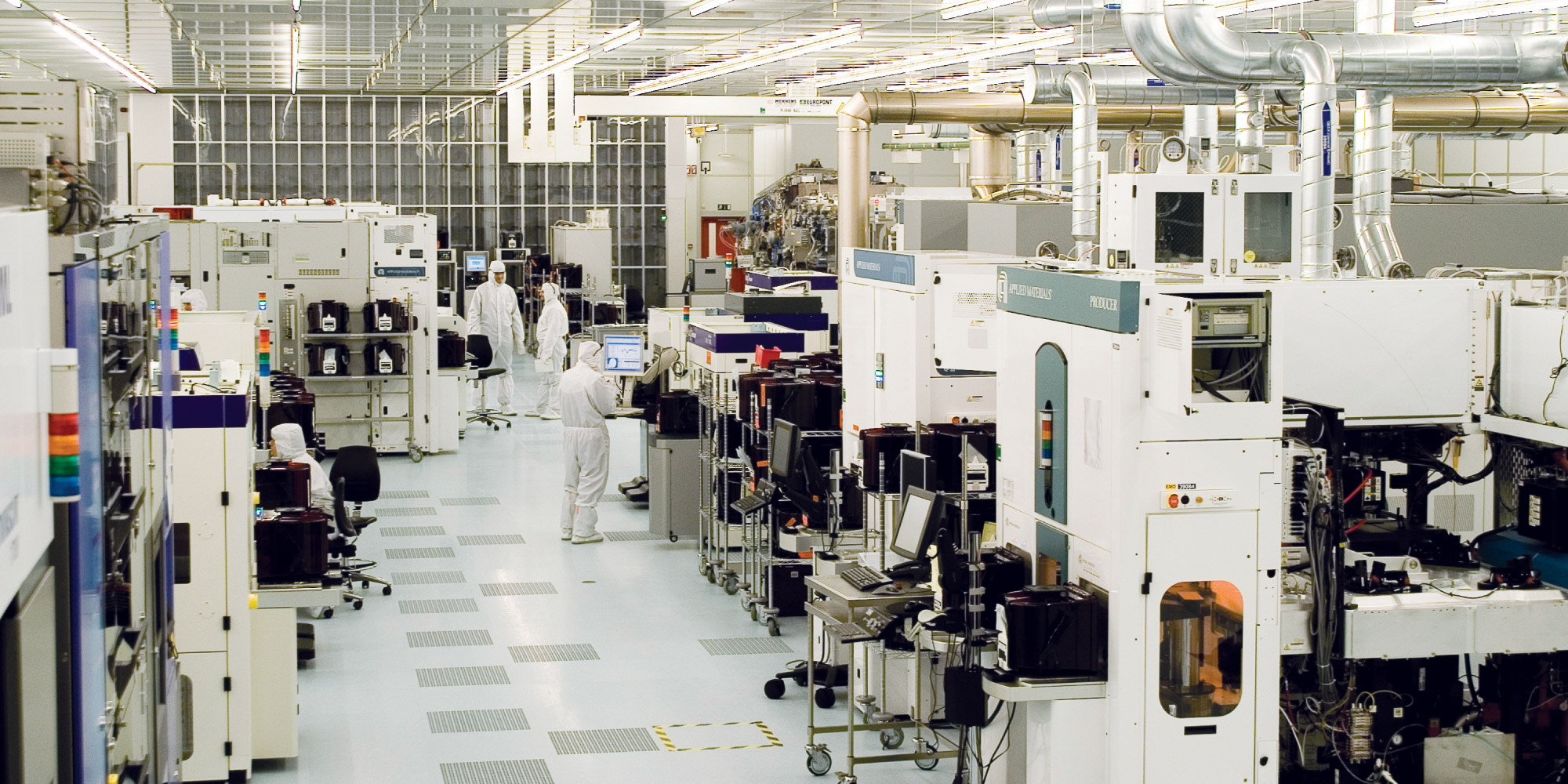

Chip designers face new challenges as well as opportunities in producing the next generation of a semiconductors as technology continues to evolve at an exponential rate. Moore’s Law, which projected that a number of transistors on the integrated circuits will double every 2 years, is slowing as physical boundaries are reached. However, new materials and fabrication techniques are enabling continued progress. This article will explore some of the major trends such as vlsi system on chip design that chip designers are exploring to push the boundaries of performance, power efficiency, and functionality in the coming years.

-

3D Chip Stacking and Integration

One approach to continue increasing transistor density within chips is to move to three-dimensional chip designs and stacking. Rather than simply making individual transistors smaller on a two-dimensional silicon substrate, 3D chip designs allow for multiple layers of active components to be placed on top of one another.

This expands the surface area available for circuits without increasing the physical footprint of the chip. Advanced packaging techniques now allow different components like memory, logic circuits, and graphics processors to be vertically integrated in a single package. Chips can also be stacked and interconnected using through-silicon vias (TSVs) that pass connections vertically through the silicon.

3D chip stacking is becoming increasingly common in applications like mobile devices where power efficiency and performance per unit area are critical. Looking ahead, continued miniaturization of TSVs and development of new bonding and interconnect technologies will be important to fully unlock the potential of 3D chip designs.

-

New Materials and Channel Materials

As the limits of silicon-based CMOS technology are approached, chip designers are exploring new channel materials to enable continued transistor scaling. Materials like gallium nitride, germanium, and even graphene are being investigated as potential replacements for silicon in future transistor designs.

These alternative channel materials have properties like higher electron mobility that allow for faster switching times. Designing transistors using these new materials requires overcoming manufacturing challenges, but progress is being made incorporating them into mainstream CMOS flows.

Long term, more exotic materials like carbon nanotubes or 2D materials may find their way into commercial chips if challenges around wafer-scale production can be solved. Advances in materials will be crucial to continue driving performance gains from one generation of chips to the next.

-

Optical Interconnects and Photonic Integration

As chip complexity increases with more cores and components, the wiring and interconnects between different parts of chips is becoming a major limitation. Electrical interconnects struggle to keep pace with the bandwidth demands as feature sizes shrink. Photonic and optical interconnect technologies are being explored as a way to overcome this bottleneck.

Optical interconnects can transmit signals at the speed of light versus the slower electrical signals. Researchers are working on ways to efficiently generate, modulate, route and detect optical signals directly on vlsi solutions silicon chips. This could involve integrating silicon photonics, plasmonics, or even quantum dot technologies.

Fully incorporating optical and photonic components into mainstream CMOS flows remains a challenge, but even hybrid approaches that use optics only for certain high-bandwidth links show promise. Longer term, the prospect of fully photonic chips that transmit all signals optically could revolutionize chip design.

-

New Computing Paradigms

As the limits of traditional von Neumann architecture are reached, chip designers are exploring new computing paradigms that better mimic the parallel, distributed processing of the human brain. Approaches like neuromorphic computing aim to design circuits and systems that are inspired by neural biology.

Rather than traditional digital logic, neuromorphic chips use large numbers of analog circuits and memory elements to mimic the behavior of biological neurons and synapses. This could enable new applications in areas like pattern recognition, control systems, and cognitive computing. Other novel approaches include quantum computing, which promises exponential speedups for certain classes of problems.

While full-scale quantum computers remain far off, some companies are working on hybrid classical-quantum systems that could demonstrate speedups for real applications in the nearer term. Realizing these new computing paradigms will require innovations not just in materials and device physics, but also new programming models, algorithms, and software tools.

-

Energy Efficiency and Heterogeneous Computing

As portable electronic devices have become more powerful, battery life has become an even greater concern for users. Chip designers are constantly challenged to improve the energy efficiency of semiconductors in order to satisfy both performance and battery life demands. At the device level, new transistor architectures like stacked nanowire designs are being implemented to reduce power consumption during operation. Alternative channel materials with improved charge mobility properties also allow circuits to switch states using less energy.

However, another important approach is utilizing heterogeneous system architectures that combine general purpose CPUs with specialized co-processors. GPUs are well-suited for graphics workloads, DSPs are optimized for signal processing tasks, and neural processors can execute AI computations much more efficiently. By offloading specific tasks to the most suitable type of core, overall system energy usage can be decreased significantly. The key challenge is programming such heterogeneous systems in a seamless, user-friendly way.

Efficient partitioning and scheduling of workloads across different core types requires careful hardware-software codesign. Runtime frameworks also need sophisticated optimization to ensure specialized accelerators are fully leveraged without excessive overhead. With further development of heterogeneous computing models and optimization techniques, chip designers hope to continue improving device energy efficiency through both specialized hardware and smarter software utilization. This will help sustain the pace of technological advancement within practical power consumption limits.

Conclusion

Chip design is entering an era of unprecedented innovation as both opportunities and challenges emerge from fundamental limits in traditional silicon technology. Advances in materials, device architectures, photonic integration, and new computing paradigms of embedded solution company hold promise to continue driving performance and efficiency gains. To fully exploit the potential of these developing technologies, multidisciplinary innovations in the fields of materials science, and device physics, as well as circuit design, along with architecture, and the software will be required. With ongoing advancement, even tiny, low-power circuits will have capabilities that are well beyond what is currently feasible in a few years. For the scientists and engineers trying to advance semiconductor technology, exciting times are ahead.

Author Bio:

I am a passionate blogger. I love to share my thoughts and ideas through blog posting. I have five years of experience in Tech, Business, & Health. I am associated with,,,.Businesssearchworld.com, marketyourbusinesses.com, worldglobalbusiness.com, Universalbusinessnews.com, digitalbusinessinsight.com, bestfinanceinsight.com, Allfinanceguide.com, financegrowthnews.com, thefinancerush.com, thefinancesuccess.com, newshealthtime.com.